# UltraSPARC T2<sup>TM</sup> Supplement to the *UltraSPARC Architecture* 2007

Draft D1.4.2, 01 Aug 2007

Privilege Levels: Privileged

Privileged and Nonprivileged

Distribution: Public

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Part No: 950-5556-01 Revision: Draft 1.4.2, 01 Aug 2007 Copyright 2002–2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 USA. All rights reserved.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape Communicator<sup>™</sup>, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved.

Sun, Sun Microsystems, the Sun logo, Solaris, and VIS are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun<sup>TM</sup> Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

**RESTRICTED RIGHTS**: Use, duplication, or disclosure by the U.S. Government is subject to restrictions of FAR 52.227-14(g)(2)(6/87) and FAR 52.227-19(6/87), or DFAR 252.227-7015(b)(6/95) and DFAR 227.7202-3(a).

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2002–2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 Etats-Unis. Tous droits réservés.

Des parties de ce document est protégé par un copyright© 1994 SPARC International, Inc.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a. Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Sun, Sun Microsystems, le logo de Sun, Solaris, et VIS sont des marques de fabrique ou des marques déposées, ou marques de service, de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays. Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une licence non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

CETTE PUBLICATION EST FOURNIE "EN L'ETAT" ET AUCUNE GARANTIE, EXPRESSE OU IMPLICITE, N'EST ACCORDEE, Y COMPRIS DES GARANTIES CONCERNANT LA VALEUR MARCHANDE, L'APTITUDE DE LA PUBLICATION A REPONDRE A UNE UTILISATION PARTICULIERE, OU LE FAIT QU'ELLE NE SOIT PAS CONTREFAISANTE DE PRODUIT DE TIERS. CE DENI DE GARANTIE NE S'APPLIQUERAIT PAS, DANS LA MESURE OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.

# Contents

| 1 | Ultr | aSPARC     | T2 Basics                                 | <br>1    |

|---|------|------------|-------------------------------------------|----------|

|   | 1.1  | Backgro    | ound                                      | <br>1    |

|   | 1.2  | 0          | ARC T2 Overview                           |          |

|   | 1.3  |            | ARC T2 Components                         |          |

|   | 110  | 1.3.1      | SPARC Physical Core                       |          |

|   |      | 1.3.2      | L2 Cache                                  |          |

|   |      | 1.3.3      | Memory Controller Unit (MCU)              |          |

|   |      | 1.3.4      | Noncacheable Unit (NCU)                   |          |

|   |      | 1.3.5      | System Interface Unit (SIU)               |          |

|   |      | 1.3.6      | SSI ROM Interface (SSI)                   |          |

| 2 | Data | a Formats  |                                           | <br>7    |

|   |      |            |                                           |          |

| 3 | Reg  |            |                                           |          |

|   | 3.1  | Ancillar   | ry State Registers (ASRs)                 |          |

|   |      | 3.1.1      | Tick Register (TICK)                      |          |

|   |      | 3.1.2      | Program Counter (PC)                      |          |

|   |      | 3.1.3      | Floating-Point State Register (FSR)       |          |

|   |      | 3.1.4      | General Status Register (GSR)             |          |

|   |      | 3.1.5      | Software Interrupt Register (SOFTINT)     |          |

|   |      | 3.1.6      | Tick Compare Register (TICK_CMPR)         |          |

|   |      | 3.1.7      | System Tick Register (STICK)              |          |

|   |      | 3.1.8      | System Tick Compare Register (STICK_CMPR) |          |

|   | 3.2  | Privileg   | ed PR State Registers                     |          |

|   |      | 3.2.1      | Trap State Register (TSTATE)              |          |

|   |      | 3.2.2      | Processor State Register (PSTATE)         |          |

|   |      | 3.2.3      | Trap Level Register (TL)                  |          |

|   |      | 3.2.4      | Current Window Pointer (CWP) Register     |          |

|   |      | 3.2.5      | Global Level Register (GL)                | <br>16   |

| 4 | Inst | ruction Fo | ormat                                     | <br>. 17 |

| 5 | Inst | ruction D  | Pefinitions                               | <br>. 19 |

|   |      |            |                                           |          |

|          | 5.1<br>5.2<br>5.3                  | Instruction Set Summary         UltraSPARC T2-Specific Instructions         Block Load and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                                                    |

|----------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|          |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| 6        | 6.1<br>6.2<br>6.3                  | s<br>Trap Levels<br>Trap Behavior<br>Trap Masking.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>31                                                                                              |

| 7        | Inter                              | rrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                                    |

|          | 7.1                                | CPU Interrupt Registers.7.1.1Interrupt Queue Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 8        | Men                                | nory Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                    |

|          | 8.1                                | Supported Memory Models           8.1.1         TSO           8.1.2         RMO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 42                                                                                                  |

| 9        | Add                                | ress Spaces and ASIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                    |

|          | 9.1                                | Address Spaces       9.1.1       48-bit Virtual and Real Address Spaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|          | 9.2                                | Alternate Address Spaces<br>9.2.1 ASI_REAL, ASI_REAL_LITTLE, ASI_REAL_IO, and<br>ASI_REAL_IO_LITTLE 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                                                                                                    |

|          |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

|          |                                    | 9.2.2 ASI_SCRATCHPAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 53                                                                                                  |

| 10       | Perf                               | 9.2.2 ASI_SCRATCHPAD ormance Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 10       | <b>Perf</b><br>10.1                | ormance Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                                                                                                    |

| 10       |                                    | ormance Instrumentation<br>SPARC Performance Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55                                                                                                    |

| 10<br>11 | 10.1<br>10.2                       | ormance Instrumentation<br>SPARC Performance Control Register<br>SPARC Performance Instrumentation Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>55</b><br>55<br>60                                                                                 |

|          | 10.1<br>10.2                       | ormance Instrumentation<br>SPARC Performance Control Register<br>SPARC Performance Instrumentation Counter<br>lementation Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55<br>55<br>60<br>63                                                                                  |

|          | 10.1<br>10.2<br>Imp                | ormance Instrumentation         SPARC Performance Control Register         SPARC Performance Instrumentation Counter         Iementation Dependencies         SPARC V9 General Information         11.1.1       Level-2 Compliance (Impdep #1).                                                                                                                                                                                                                                                                                                                                                            | 55<br>60<br>63<br>63<br>63                                                                            |

|          | 10.1<br>10.2<br>Imp                | ormance Instrumentation         SPARC Performance Control Register         SPARC Performance Instrumentation Counter         lementation Dependencies         SPARC V9 General Information         11.1.1       Level-2 Compliance (Impdep #1).         11.1.2       Unimplemented Opcodes, ASIs, and ILLTRAP                                                                                                                                                                                                                                                                                              | 55<br>60<br>63<br>63<br>63<br>63<br>63                                                                |

|          | 10.1<br>10.2<br>Imp                | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counterlementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1)11.1.2Unimplemented Opcodes, ASIs, and ILLTRAP11.1.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)                                                                                                                                                                                                                                                                                                               | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63                                                          |

|          | 10.1<br>10.2<br>Imp                | ormance Instrumentation         SPARC Performance Control Register         SPARC Performance Instrumentation Counter         lementation Dependencies         SPARC V9 General Information         11.1.1       Level-2 Compliance (Impdep #1).         11.1.2       Unimplemented Opcodes, ASIs, and ILLTRAP                                                                                                                                                                                                                                                                                              | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64                                        |

|          | 10.1<br>10.2<br>Imp                | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counterlementation DependenciesInformation11.1.1Level-2 Compliance (Impdep #1)11.1.2Unimplemented Opcodes, ASIs, and ILLTRAP11.1.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.1.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.1.5Secure Software11.1.6Operation in Nonprivileged Mode with TL > 0                                                                                                                                                                                                      | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>64                            |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counterlementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1)11.2Unimplemented Opcodes, ASIs, and ILLTRAP11.1.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.1.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.1.5Secure Software11.1.6Operation in Nonprivileged Mode with TL > 011.1.7Address Masking (Impdep #125)                                                                                                                                                    | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>64<br>64                |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counter.lementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1).11.2Unimplemented Opcodes, ASIs, and ILLTRAP.11.1.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.1.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.1.5Secure Software11.1.6Operation in Nonprivileged Mode with TL > 0.11.1.7Address Masking (Impdep #125).SPARC V9 Integer Operations.                                                                                                                   | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>64<br>65                      |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counter.lementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1).11.2Unimplemented Opcodes, ASIs, and ILLTRAP.11.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.5Secure Software11.6Operation in Nonprivileged Mode with TL > 0.11.7Address Masking (Impdep #125).SPARC V9 Integer Operations.11.2.1Integer Register File and Window Control Registers (Impdep #                                                           | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>64<br>64<br>65<br>2) 65             |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counter.lementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1).11.2Unimplemented Opcodes, ASIs, and ILLTRAP.11.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.5Secure Software11.6Operation in Nonprivileged Mode with TL > 0.11.7Address Masking (Impdep #125).SPARC V9 Integer Operations.11.2.1Integer Register File and Window Control Registers (Impdep #11.2.2Clean Window Handling (Impdep #102)                  | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>64<br>64<br>65<br>2).65<br>65 |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counter.lementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1).11.1.2Unimplemented Opcodes, ASIs, and ILLTRAP.11.1.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.1.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.1.5Secure Software11.1.6Operation in Nonprivileged Mode with TL > 0.11.1.7Address Masking (Impdep #125).SPARC V9 Integer Operations.11.2.1Integer Register File and Window Control Registers (Impdep #11.2.3Integer Multiply and Divide11.2.4MULScc. | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>65<br>65    |

|          | 10.1<br>10.2<br><b>Imp</b><br>11.1 | ormance InstrumentationSPARC Performance Control RegisterSPARC Performance Instrumentation Counter.lementation DependenciesSPARC V9 General Information11.1.1Level-2 Compliance (Impdep #1).11.2Unimplemented Opcodes, ASIs, and ILLTRAP.11.3Trap Levels (Impdep #37, 38, 39, 40, 114, 115)11.4Trap Handling (Impdep #16, 32, 33, 35, 36, 44)11.5Secure Software11.6Operation in Nonprivileged Mode with TL > 0.11.7Address Masking (Impdep #125).SPARC V9 Integer Operations.11.2.1Integer Register File and Window Control Registers (Impdep #11.2.3Integer Multiply and Divide                          | 55<br>60<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>66                |

|    |                                      | 11.3.3                                                                                                                                                                                | Quad-Precision Floating-Point Operations (Impdep #3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                           |

|----|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|    |                                      | 11.3.4                                                                                                                                                                                | Floating-Point Upper and Lower Dirty Bits in FPRS Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                                                        |

|    |                                      | 11.3.5                                                                                                                                                                                | Floating-Point Status Register (FSR) (Impdep #13, 19, 22, 23, 24)                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68                                                                                        |

|    | 11.4                                 | SPARC <sup>*</sup>                                                                                                                                                                    | V9 Memory-Related Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                           |

|    |                                      | 11.4.1                                                                                                                                                                                | Load/Store Alternate Address Space (Impdep #5, 29, 30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68                                                                                        |

|    |                                      | 11.4.2                                                                                                                                                                                | Read/Write ASR (Impdep #6, 7, 8, 9, 47, 48)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

|    |                                      | 11.4.3                                                                                                                                                                                | MMU Implementation (Impdep #41)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |

|    |                                      | 11.4.4                                                                                                                                                                                | FLUSH and Self-Modifying Code (Impdep #122)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

|    |                                      | 11.4.5                                                                                                                                                                                | PREFETCH{A} (Impdep #103, 117)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                                                        |

|    |                                      | 11.4.6                                                                                                                                                                                | LDD/STD Handling (Impdep #107, 108)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

|    |                                      | 11.4.7                                                                                                                                                                                | FP mem_address_not_aligned (Impdep #109, 110, 111, 112)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70                                                                                        |

|    |                                      | 11.4.8                                                                                                                                                                                | Supported Memory Models (Impdep #113, 121)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                                                                                        |

|    |                                      | 11.4.9                                                                                                                                                                                | Implicit ASI When TL > 0 (Impdep #124)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                        |

|    | 11.5                                 | Non-SPA                                                                                                                                                                               | ARC V9 Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 71                                                                                      |

|    |                                      | 11.5.1                                                                                                                                                                                | Cache Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71                                                                                        |

|    |                                      | 11.5.2                                                                                                                                                                                | Block Memory Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                                                        |

|    |                                      | 11.5.3                                                                                                                                                                                | Partial Stores.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71                                                                                        |

|    |                                      | 11.5.4                                                                                                                                                                                | Short Floating-Point Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                                                                                        |

|    |                                      | 11.5.5                                                                                                                                                                                | Load Twin Extended Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                           |

|    |                                      | 11.5.6                                                                                                                                                                                | UltraSPARC T2 Instruction Set Extensions (Impdep #106)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

|    |                                      | 11.5.7                                                                                                                                                                                | Performance Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                        |

| 12 | Mem                                  | ory Man                                                                                                                                                                               | agement Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 73                                                                                      |

|    |                                      |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |

|    | 12.1                                 | Translat                                                                                                                                                                              | ion Table Entry (TTE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 73                                                                                      |

|    | 12.1<br>12.2                         |                                                                                                                                                                                       | ion Table Entry (TTE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |

|    |                                      | Translat                                                                                                                                                                              | ion Storage Buffer (TSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 75                                                                                      |

|    | 12.2                                 | Translat<br>MMU-R                                                                                                                                                                     | ion Storage Buffer (TSB)<br>elated Faults and Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 75<br>. 76                                                                              |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1                                                                                                                                                           | ion Storage Buffer (TSB)<br>elated Faults and Traps<br>IAE_privilege_violation Trap                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 75<br>. 76<br>76                                                                        |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2                                                                                                                                                 | ion Storage Buffer (TSB)<br>elated Faults and Traps<br>IAE_privilege_violation Trap<br>IAE_nfo_page Trap                                                                                                                                                                                                                                                                                                                                                                                                                     | . 75<br>. 76<br>76<br>76                                                                  |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1                                                                                                                                                           | ion Storage Buffer (TSB)<br>elated Faults and Traps<br>IAE_privilege_violation Trap<br>IAE_nfo_page Trap<br>instruction_address_range Trap                                                                                                                                                                                                                                                                                                                                                                                   | . 75<br>. 76<br>76<br>76<br>76                                                            |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3                                                                                                                                       | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap                                                                                                                                                                                                                                                                                                                        | . 75<br>. 76<br>76<br>76<br>76<br>76                                                      |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4                                                                                                                             | ion Storage Buffer (TSB)<br>elated Faults and Traps<br>IAE_privilege_violation Trap.<br>IAE_nfo_page Trap<br>instruction_address_range Trap<br>instruction_real_range Trap<br>DAE_privilege_violation Trap                                                                                                                                                                                                                                                                                                                   | . 75<br>. 76<br>76<br>76<br>76<br>76<br>76                                                |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5                                                                                                                   | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap                                                                                                                                                                                                                                                                                                                        | . 75<br>. 76<br>76<br>76<br>76<br>76<br>77                                                |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6                                                                                                         | ion Storage Buffer (TSB)<br>telated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap                                                                                                                                                                                                                                            | . 75<br>76<br>76<br>76<br>76<br>76<br>77<br>77                                            |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7                                                                                               | ion Storage Buffer (TSB)<br>telated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap<br><i>DAE_nc_page</i> Trap                                                                                                                                                                                                                 | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77                          |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8                                                                                     | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>DAE_nfo_page</i> Trap                                                                   | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77              |

|    | 12.2                                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9                                                                           | ion Storage Buffer (TSB)<br>telated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap                                                                                                                                                      | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77              |

|    | 12.2<br>12.3                         | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11                                                     | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap.<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap.<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>privileged_action</i> Trap.<br>*_mem_address_not_aligned Traps<br>Description                                                                 | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77        |

|    | 12.2<br>12.3<br>12.4                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C                                            | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap.<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap.<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>DAE_nfo_page</i> Trap.<br><i>privileged_action</i> Trap.<br>*_mem_address_not_aligned Traps                                                   | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77        |

|    | 12.2<br>12.3<br>12.4                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C                                            | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap.<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap.<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>privileged_action</i> Trap.<br>*_mem_address_not_aligned Traps<br>Description                                                                 | . 75<br>. 76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>7 |

|    | 12.2<br>12.3<br>12.4                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C<br>Translat                                | ion Storage Buffer (TSB)<br>telated Faults and Traps<br><i>IAE_privilege_violation</i> Trap<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap<br><i>DAE_nc_page</i> Trap<br><i>DAE_invalid_asi</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>privileged_action</i> Trap<br>*_mem_address_not_aligned Traps<br>prevision                                                                     | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77        |

|    | 12.2<br>12.3<br>12.4                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C<br>Translat                                | <pre>ion Storage Buffer (TSB)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 75<br>. 76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>7 |

|    | 12.2<br>12.3<br>12.4                 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C<br>Translat<br>12.5.1<br>12.5.2            | <pre>ion Storage Buffer (TSB)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>77        |

|    | 12.2<br>12.3<br>12.4<br>12.5         | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C<br>Translat<br>12.5.1<br>12.5.2<br>Complia | <pre>ion Storage Buffer (TSB)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77        |

|    | 12.2<br>12.3<br>12.4<br>12.5<br>12.6 | Translat<br>MMU-R<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>12.3.6<br>12.3.7<br>12.3.8<br>12.3.9<br>12.3.10<br>12.3.11<br>MMU C<br>Translat<br>12.5.1<br>12.5.2<br>Complia | ion Storage Buffer (TSB)<br>elated Faults and Traps<br><i>IAE_privilege_violation</i> Trap.<br><i>IAE_nfo_page</i> Trap<br><i>instruction_address_range</i> Trap<br><i>instruction_real_range</i> Trap<br><i>DAE_privilege_violation</i> Trap<br><i>DAE_side_effect_page</i> Trap.<br><i>DAE_nc_page</i> Trap<br><i>DAE_nc_page</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>DAE_nfo_page</i> Trap<br><i>privileged_action</i> Trap.<br>*_mem_address_not_aligned Traps<br>Data Translation<br>ance With the SPARC V9 Annex F. | . 75<br>76<br>76<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>77        |

| Α | Progr | amming (       | Guidelines                                                                 |                                                                                                                                         |     |

|---|-------|----------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | A.1   | Multithr       | eading                                                                     |                                                                                                                                         |     |

|   | A.2   | Instructi      | on Latency                                                                 | ·····                                                                                                                                   |     |

| B | IEEE  | 754 Floati     | ng-Point S                                                                 | upport                                                                                                                                  |     |

|   | B.1   |                | -                                                                          | andling                                                                                                                                 |     |

|   |       | B.1.1          |                                                                            | Arithmetic                                                                                                                              |     |

|   |       |                | B.1.1.1                                                                    | One Infinity Operand Arithmetic                                                                                                         |     |

|   |       |                | B.1.1.2                                                                    | Two Infinity Operand Arithmetic                                                                                                         | 101 |

|   |       | B.1.2          |                                                                            | thmetic                                                                                                                                 |     |

|   |       | B.1.3          |                                                                            | thmetic                                                                                                                                 |     |

|   |       | B.1.4          |                                                                            | nexact Exceptions                                                                                                                       |     |

|   | B.2   |                |                                                                            | 1g                                                                                                                                      |     |

|   |       | B.2.1          |                                                                            | oth Subnormal Operands                                                                                                                  |     |

|   |       | B.2.2          | Normal (                                                                   | Operand(s) Giving Subnormal Result                                                                                                      |     |

| С | Diffe | rences Fro     | om UltraSP                                                                 | PARC T1                                                                                                                                 |     |

|   | C.1   | General        | Architectu                                                                 | ral and Microarchitectural Differences                                                                                                  |     |

|   | C.2   |                |                                                                            |                                                                                                                                         |     |

|   | C.3   | MMU Di         | ifferences .                                                               |                                                                                                                                         |     |

|   | C.4   | Performa       | ance Instru                                                                | mentation Differences                                                                                                                   |     |

| D | Cache | es and Ca      | che Cohere                                                                 | ency                                                                                                                                    |     |

|   | D.1   |                |                                                                            | Interactions                                                                                                                            |     |

|   | D.2   |                |                                                                            |                                                                                                                                         |     |

|   |       | D.2.1          | Displace                                                                   | ment Flushing                                                                                                                           | 120 |

|   |       | D.2.2          |                                                                            | Accesses and Cacheability                                                                                                               |     |

|   |       | D.2.3          | Coherence                                                                  | ce Domains                                                                                                                              |     |

|   |       |                | D.2.3.1                                                                    | Cacheable Accesses                                                                                                                      |     |

|   |       |                | D.2.3.2                                                                    | Noncacheable and Side-Effect Accesses                                                                                                   |     |

|   |       | D 2 4          | D.2.3.3                                                                    | Global Visibility and Memory Ordering                                                                                                   |     |

|   |       | D.2.4          | D.2.4.1                                                                    | Synchronization: MEMBAR and FLUSH .<br>MEMBAR #LoadLoad                                                                                 |     |

|   |       |                | D.2.4.1<br>D.2.4.2                                                         | MEMBAR #LoadLoad<br>MEMBAR #StoreLoad                                                                                                   |     |

|   |       |                | D.2.4.3                                                                    | MEMBAR #LoadStore                                                                                                                       |     |

|   |       |                | D.2.4.4                                                                    | MEMBAR #StoreStore and STBAR                                                                                                            |     |

|   |       |                |                                                                            | MEMBAR #Lookaside                                                                                                                       |     |

|   |       |                | D.2.4.5                                                                    | MENIDAK #LOOKaside                                                                                                                      |     |

|   |       |                | D.2.4.5<br>D.2.4.6                                                         | MEMBAR #LOOKASIde                                                                                                                       |     |

|   |       |                |                                                                            |                                                                                                                                         |     |

|   |       |                | D.2.4.6<br>D.2.4.7<br>D.2.4.8                                              | MEMBAR #MemIssue<br>MEMBAR #Sync (Issue Barrier)<br>Self-Modifying Code (FLUSH)                                                         |     |

|   |       | D.2.5          | D.2.4.6<br>D.2.4.7<br>D.2.4.8<br>Atomic C                                  | MEMBAR #MemIssue<br>MEMBAR #Sync (Issue Barrier)<br>Self-Modifying Code (FLUSH)<br>Dperations                                           |     |

|   |       | D.2.5          | D.2.4.6<br>D.2.4.7<br>D.2.4.8<br>Atomic C<br>D.2.5.1                       | MEMBAR #MemIssue<br>MEMBAR #Sync (Issue Barrier)<br>Self-Modifying Code (FLUSH)<br>Operations<br>SWAP Instruction                       |     |

|   |       | D.2.5          | D.2.4.6<br>D.2.4.7<br>D.2.4.8<br>Atomic C<br>D.2.5.1<br>D.2.5.2            | MEMBAR #MemIssue<br>MEMBAR #Sync (Issue Barrier)<br>Self-Modifying Code (FLUSH)<br>Operations<br>SWAP Instruction<br>LDSTUB Instruction |     |

|   |       | D.2.5<br>D.2.6 | D.2.4.6<br>D.2.4.7<br>D.2.4.8<br>Atomic C<br>D.2.5.1<br>D.2.5.2<br>D.2.5.3 | MEMBAR #MemIssue<br>MEMBAR #Sync (Issue Barrier)<br>Self-Modifying Code (FLUSH)<br>Operations<br>SWAP Instruction                       |     |

| <br>E Glossary     |

|--------------------|

| <br>F Bibliography |

| <br>Index          |

•

## UltraSPARC T2 Basics

## 1.1 Background

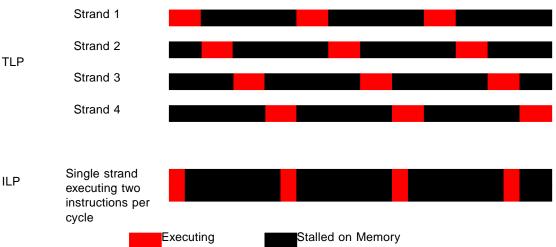

UltraSPARC T2 is the follow-on chip multi-threaded (CMT) processor to the highly successful UltraSPARC T1 processor. The UltraSPARC T1 product line fully implements Sun's Throughput Computing initiative for the horizontal system space. Throughput Computing is a technique that takes advantage of the thread-level parallelism that is present in most commercial workloads. Unlike desktop workloads, which often have a small number of threads concurrently running, most commercial workloads achieve their scalability by employing large pools of concurrent threads.